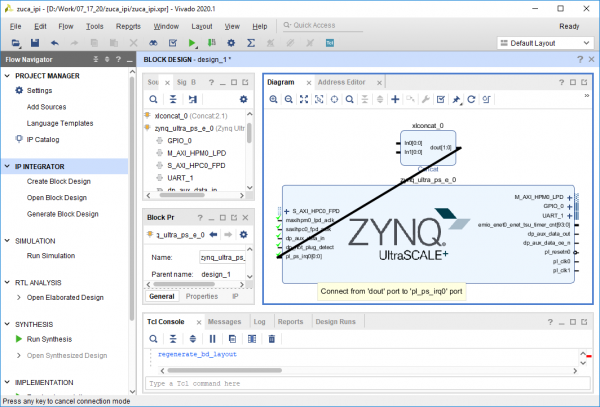

将Zynq UltraScale处理器添加到块设计中

Zynq UltraScale + MPSoC IP表示Zynq UltraScale芯片的非FPGA组件,称为处理系统或PS。它必须用于块设计,希望将任何连接到处理器,并配置PS-Side外围设备,时钟和其他设置。

笔记:本节仅适用于带有Zynq UltraScale +芯片的板。

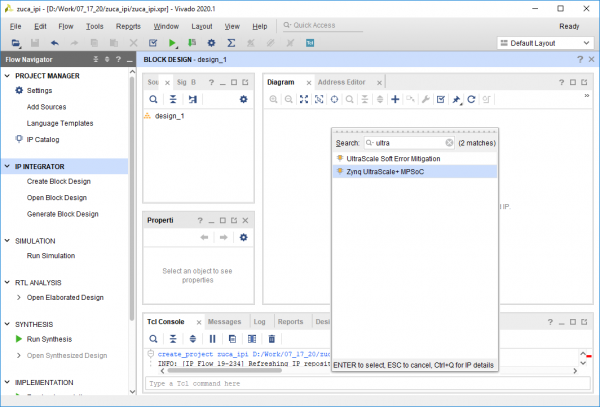

在“框图”窗格的工具栏中,单击“添加IP.按钮 ( )。

)。

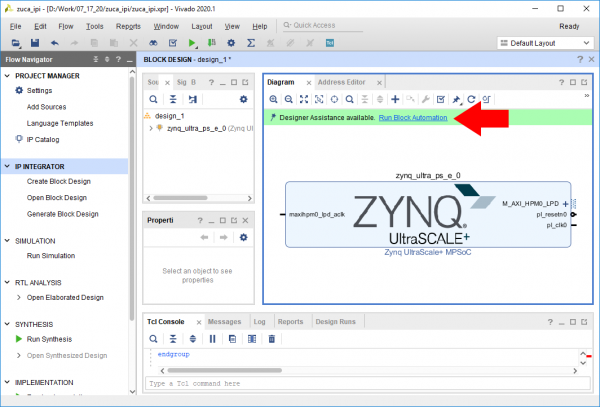

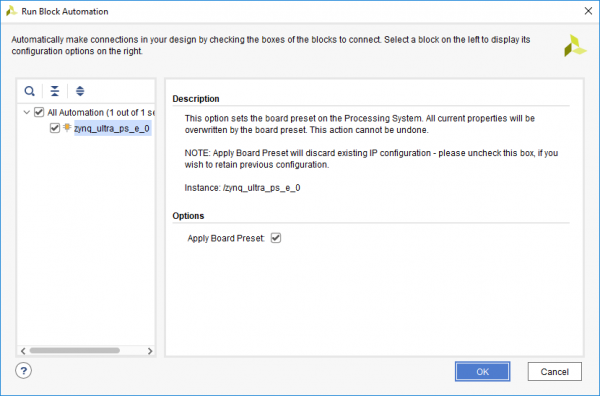

项目的需求可能要求您更改PS的一些默认设置。要编辑其设置,请双击它以打开配置向导。

以下两个具体情况下突出显示:

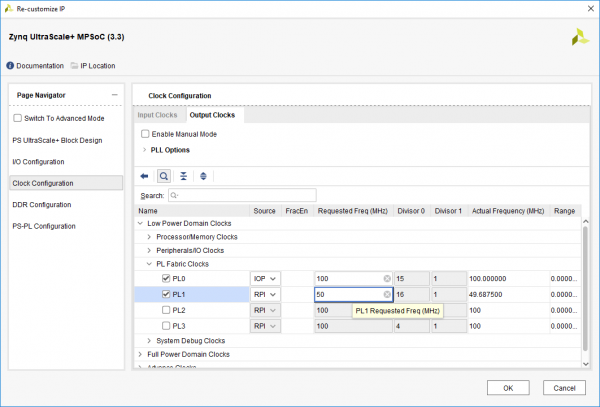

PS可以生成多个时钟,然后提供给FPGA织物。这些时钟称为PL时钟,并且可以在其中找到时钟配置MPSoC配置向导的选项卡。它们位于低功率域时钟→PL面料钟表下降。可以使用复选框启用(或禁用),可以更改用于驱动时钟的硬件源,并且可以修改频率。

Digilent Zynq UltraScale Loards的板文件默认使至少一个低功耗域PL时钟,旨在与连接到MPSoC的M_AXI_HPM0_LPD端口的外围设备一起使用。

某些设计可能需要将特定频率的额外时钟添加到您的设计中。在这些情况下,使能第二时钟并指定所需的频率,如右侧图像所示。

笔记:始终可以返回此部分,因为可以在构建硬件之前的任何时间进行附加时钟的添加。

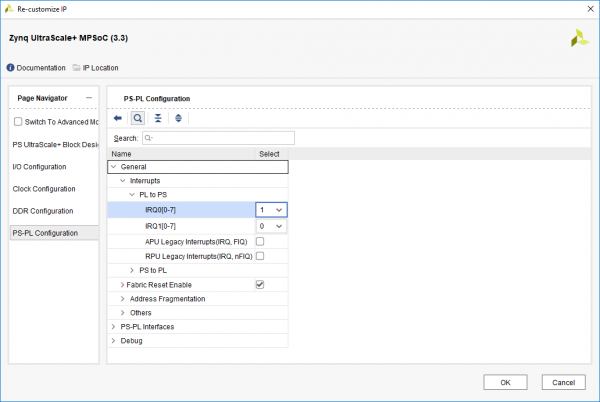

UltraScale设备还可以使用在FPGA面料中产生的中断来触发处理系统内的中断。中断相关的设置可以在配置向导中更改PS-PL配置标签。这些中断可以使用IRQ0端口,该端口可以在其中找到一般的→中断→pl到ps.下降。要启用此端口,IRQ0下拉列表应设置为“1”。