art - Microblaze服务器入门

概述

本指南将提供使用Vivado IP Integrator创建基于Microblaze的硬件设计的一步一步的演练,该集成器将构建在从Microblaze开始通过使用机载以太网端口和Arty FPGA板的gpio来指导。

在本教程的最后,你将有一个全面的Arty硬件设计,利用各种硬件端口的Arty是由Microblaze软核处理器块管理。

先决条件

技能

-

熟悉Vivado

硬件

-

附庸风雅的FPGA板

-

微型USB电缆

-

用于UART通信和JTAG编程

-

-

以太网电缆

软件

-

Xilinx Vivado 2015。Xwith the SDK package.

-

串行终端应用程序

-

在本教程中使用Tera术语

-

董事会的支持文件

-

附庸风雅的支持文件

-

这些文件将描述GPIO界面在您的板,使它更容易选择您的板在最初的设计设置和添加GPIOIP块在块设计中

-

遵循这个维基指南Vivado板文件为Digilent 7系列FPGA板关于如何安装Vivado 2015的板支持文件。X

-

介绍

Microblaze是Xilinx的软IP核,它将完全在Xilinx FPGA通用内存和逻辑结构中实现微处理器。在本教程中,我们将添加以太网功能并创建一个回显服务器。

一般的设计流程

即Vivado

-

打开Vivado并选择Arty董事会

-

创建一个新的Vivado项目

-

在新项目中创建空块设计工作区

-

使用IP积分器工具添加所需的IP块并构建硬件设计

-

验证和保存块设计

-

创建HDL系统包装器

-

运行设计综合与实现

-

生成一些文件

-

导出硬件设计,包括生成的位流文件到SDK工具

-

发射SDK

现在硬件设计被导出到SDK工具。Vivado到SDK的转换是通过Vivado内部完成的。我们将使用SDK来创建一个软件应用程序,该应用程序将使用自定义的板接口数据和FPGA硬件配置,通过导入硬件设计信息从Vivado。

2SDK

-

创建新的应用程序项目并选择默认的Hello World模板

-

FPGA程序

-

通过选择正确的UART COM端口和波特率来运行配置

教程

1.创建新项目

1.1)打开Vivado并点击创建新项目打开Vivado的新项目向导。

1.2)将打开一个新窗口,点击下一个你会看到下面的屏幕。命名您的项目(没有空格!)并在单击之前选择您的项目保存目录下一个.下划线可以很好地替代空格。

1.3)我们将从头开始构建这个项目,并添加我们自己的资源,因此我们将希望创建一个RTL项目。选择RTL项目和离开不要指定来源盒子不。点击下一个.

1.4)如果您遵循了董事会支持文件Wiki指南,然后单击下一步并选择董事会.从筛选器选项中选择供应商、显示名称和板修订。附庸风雅的应该显示在选择列表中。选择正确的板名不匹配将导致错误。

此时,你已经成功地创建了一个项目,将正确地与火炮沟通。

2.创建新的块设计

这是主项目窗口,您可以在这里创建基于IP的块设计或添加基于RTL的设计源。左边的流导航器面板提供了关于如何创建硬件设计、执行模拟、运行合成和实现以及生成位文件的多个选项。您还可以使用Hardware Manager为RTL项目生成的位文件直接从Vivado对电路板进行编程。

对于我们的设计,我们将使用IP积分器来创建一个新的块设计。

2.1)在左边,你应该看到Flow Navigator。选择创建块设计IP集成商。给你的设计起一个名字(没有任何空格),然后点击好吧.

您已经创建了一个新的块设计。

3.添加时钟和DDR3组件

3.7)点击连接自动化运行在上面的绿色横幅上。点击好吧.

Vivado将你的系统重置连接到MIG上的sys_rst。连接这个新的复位端口到resetn在时钟向导块上输入。

4.添加Microblaze处理器和配置

4.1)点击添加IP按钮和搜索Microblaze.

双击Microblaze将其添加到您的块设计中。

5.添加外围设备

5.1)进入董事会标签,并找到USB UART组件。单击并拖动将其添加到块设计中,以便将Uartlite块添加到您的设计中。

5.3)点击添加IP按钮和搜索计时器.双击AXI计时器将其添加到您的块设计中。

6.路由最后的连接

6.1)路线中断在AXI计时器块In0(0时)在Concat块。下一个路线ip2intc_irpt在AXI EthernetLite块三机一体(0时)在Concat块。

6.2)右键单击设计的背景(空白),然后点击创建端口…,或使用快捷键Ctrl-K。将此端口命名为“eth_ref_clk”,并将选项更改为下图中的选项。点击好吧一旦完成。

7.验证设计并制作HDL包装器

7.2)选择验证设计.这将检查设计和连接错误。

在设计验证步骤之后,我们将继续创建一个HDL系统包装器。点击来源标签和找到你的块设计。

7.4)右键单击你的方块设计,然后单击创建高密度脂蛋白包装.让Vivado管理包装和自动更新并点击好吧.

这将在VHDL中创建一个顶级模块,并允许您生成位流。

8.约束Eth_ref_clk

我们现在必须通过创建一个XDC文件将eth_ref_clk引脚连接到FPGA上的正确引脚。下设计窗口中,选择来源选项卡。扩大属文件夹,右击若干并点击添加来源…

8.2)选择“添加或创建约束”,单击下一个.

8.3)点击创建文件…,命名新的约束文件并单击好吧然后完成.

打开新的约束文件,粘贴如下代码行:set_property -dict {PACKAGE_PIN G18 IOSTANDARD LVCMOS33} [get_ports {eth_ref_clk}];#同步信道= eth_ref_clk

完成后保存XDC文件。

8.生成一些文件

8.1)在Vivado的顶部工具栏中,单击产生的比特流.这也可以在流导航器面板在左边,下面程序和调试.

如果您还没有保存您的设计,您将得到一个提示,以保存块设计。

将开始生成位文件。工具会运行合成和实现.在合成和实现都成功完成后,将创建位文件。你会发现在项目窗口的右上角运行着一个Synthesis and Implementation的状态栏。

这个过程可以从任何地方5至60分钟这取决于你的电脑。

8.3)位流生成完成后,屏幕上会弹出提示信息。您不必为此演示打开已实现设计。点击取消.

9.导出硬件设计到SDK

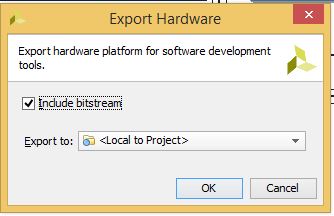

9.1)在主工具栏上,单击文件并选择出口的硬件.勾选复选框包括比特流并点击好吧.这将导出硬件设计与系统包装软件开发工具- Vivado SDK。

下面将创建一个新的文件目录echo_server。SDK类似Vivado的硬件设计项目名称。另外两个文件,.sysdef和.hdf也创造了。这个步骤实际上创建了一个新的SDK工作区。

9.2)在主工具栏上,单击文件→启动SDK.将这两个下拉菜单保留为默认值本地项目并点击好吧.这将打开Xilinx SDK并导入硬件。

10.在Xilinx SDK

10.1)硬件设计规范和包含的IP块显示在system.hdf文件。Xilinx SDK独立于Vivado,也就是说,从现在开始,您可以在导出的HW设计之上用C/ c++创建您的SW项目。如果有必要,您还可以直接从Vivado Project主目录中创建的SDK文件夹启动SDK。

从这里开始,如果你需要返回Vivado并对HW设计进行更改,那么建议关闭SDK窗口并在Vivado中进行所需的HW设计编辑。在此之后,您必须遵循创建新的HDL包装器、保存设计和位文件生成的顺序。这个新的位文件和系统包装器必须被导出到SDK中。

10.2)中Project Explorer标签在左边,你可以看到你的硬件平台。

系统是在Vivado中创建的块设计的名称。该硬件平台具有所有的HW设计定义、已添加的IP接口、外部输出信号信息和本地内存地址信息。

11.在SDK中创建新的应用程序项目

11.1)点击新下拉箭头和选择应用程序项目.

为项目指定一个没有空格的名称,然后单击下一个.

11.2)选择lwIP回显服务器从模板列表中单击好吧.

您将看到两个新文件夹Project Explorer面板。

- - - - - -echo_server包含所有二进制文件,.C和.H(头文件)

- - - - - -echo_server_bsp哪个是支持板文件夹

echo_server是我们的主要工作源文件夹。这里还包含一个重要的文件,它是lscript.ld.这是一个Xilinx自动生成的链接器脚本文件。双击此文件打开。

11.3)回到Project Explorer,双击并打开system.mss下echo_server_bsp文件夹中。点击修改此BSP的设置.

11.4)点击lwip141然后找到temac_adapter_options点击箭头。找到phy_link_speed并将“Value”修改为CONFIG_LINKSPEED100.点击好吧.

12.用位文件编程FPGA

12.1)确认火炮已通过micro USB接口与主机相连。如果连接正确,红色电源领导应该打开。在顶部工具栏上,单击FPGA程序按钮。

12.2)点击程序使用硬件设计对FPGA进行编程。

13.设置UART终端

13.1)打开一个串行终端应用程序(Tera术语)。连接到波特率为9600的Arty UART端口。通过双击Uartlite模块,可以在模块设计中改变波特率。

1.对Microblaze处理器进行编程

在开始之前,确保你的Arty已经插入了路由器。

14.2)回到SDK,选择你的echo_server项目,并单击运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

15.使用Tera Term测试服务器

15.1)用以太网线将PC连接到Zybo。如果使用路由器,观察UART控制台找出Zybo回显服务器的IP,并连接到该IP地址。将连接设置为静态是不必要的。

15.2)为了从您的计算机直接连接到echo服务器,您必须设置一个静态IP地址的以太网连接。要做到这一点:

记得回到开放网络和共享中心

选择Internet协议版本4 (TCP/IPv4)并点击属性.

选择自动获取IP地址

添加IP按钮和搜索Microblaze.

添加IP按钮和搜索Microblaze.

重新布局按钮重新安排您的块设计。

重新布局按钮重新安排您的块设计。

验证设计.这将检查设计和连接错误。

验证设计.这将检查设计和连接错误。

产生的比特流.这也可以在流导航器面板在左边,下面程序和调试.

产生的比特流.这也可以在流导航器面板在左边,下面程序和调试.

新下拉箭头和选择应用程序项目.

新下拉箭头和选择应用程序项目.

FPGA程序按钮。

FPGA程序按钮。

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.