Genesys 2 -开始使用Microblaze服务器

注意:Genesys2使用千兆以太网模块,需要TEMAC IP即没有包含在Vivado Webpack中.为了完成本教程,您必须购买TEMAC IP的许可证或通过以下方式从他们的网站免费获得评估许可证本指南.

概述

本指南将逐步介绍如何使用Vivado IP Integrator构建基于Microblaze的硬件设计开始使用Microblaze通过使用Genesys2 FPGA板上的以太网端口和gpio来引导。

在本教程的最后,您将有一个全面的硬件设计,为Genesys2,利用Genesys2上的各种硬件端口,这些端口由Microblaze软核处理器块管理。

注意:Genesys2需要Vivado设计版或系统版,支持Kintex-7 FPGA。这和免费的webpack版本不一样

先决条件

硬件

-

Digilent Genesys2 FPGA板

-

2 Micro USB cable用于UART通信和JTAG编程

-

以太网电缆

软件

-

Xilinx Vivado 2015。X

-

支持Kintex-7 FPGA必须安装系统版本或设计版本

-

-

Xilinx SDK

-

与Vivado安装的版本相同

-

-

串行终端应用程序

-

在本教程中使用Tera术语

-

-

安装TEMAC IP许可

-

遵循这个维基指南:安装TEMAC IP的120天评估License.

-

董事会的支持文件

-

董事会的支持文件-这些文件将描述GPIO接口,并使您更容易选择您的FPGA板和添加GPIOIP块。

-

遵循这个维基指南Digilent 7系列FPGA板的Vivado板文件关于如何安装Vivado 2015的板支持文件。X

-

教程

1.创建项目

当您第一次运行Vivado时,这将是主启动窗口,您可以在这里创建一个新项目或打开一个最近的项目。

1.1)点击创建新项目.选择项目名称和位置,以便有没有空格.对于项目名称、文件名和位置路径,这是一个重要的命名约定。

下划线可以很好地代替空格。

为Vivado项目创建一个专用文件夹是一种很好的实践,最好使用最小的路径长度。例如:C: / Vivado_Projects。

命名项目并选择项目位置并单击下一个.

1.2)选择项目类型为RTL项目.不选中“不指定源”框并单击下一个.

1.3)我们不会在这里导入或创建任何文件,所以单击下一个直到零件选择屏幕。

1.5)显示新项目设计源和目标设备的概要。点击完成.

2.创建新的区块设计

这是一个主项目窗口,在这里你可以创建一个基于IP的块设计或者添加基于RTL的设计源。左边的流量导航面板提供了关于如何创建硬件设计、执行模拟、运行合成和实现以及生成位文件的多个选项。您还可以使用硬件管理器直接从Vivado使用为RTL项目生成的位文件来编写电路板。

对于我们的设计,我们将使用IP积分器创建一个新的块设计。

2.1)在左边,你应该看到Flow Navigator。选择创建块设计IP集成商。给你的设计一个名字(不要有任何空白),然后点击好吧.

您已经创建了一个新的模块设计。

3.添加DDR3组件

3.1)点击董事会标签(下面用橙色突出显示)

此列表包含您之前安装的board文件中定义的所有组件。这些已经配置为与几个Vivado ip一起工作。

3.2)单击并拖动的DDR3 SDRAM组件添加到空块设计中。Vivado将自动连接DDR3 SDRAM和系统时钟到MIG IP。

3.3)点击连接自动化运行在上面的绿色横幅上。点击好吧.

Vivado将在MIG上将你的系统重置连接到sys_rst。

4.添加Microblaze处理器和配置

4.1)点击添加IP按下并搜索Microblaze.

双击Microblaze将其添加到您的块设计中。

4.2)点击块自动化运行打开Microblaze处理器的Block自动化。

在这里,您可以选择给Microblaze处理器提供多少内存。配置选项要匹配下面的图片,请单击好吧.

4.3)运行区块自动化将自动生成一组额外的IP区块,这些IP区块将根据上一步选择的选项自动添加到我们的硬件设计中。暂时不要单击“运行连接自动化”。

5.添加外围组件

5.1)进入董事会再次制表,找到USB UART组件。单击并拖动将Uartlite块添加到设计中。

5.2)找到以太网PHY和将其拖到块设计上将以太网块添加到您的设计中。

5.3)点击添加IP按下并搜索计时器.双击AXI计时器将其添加到您的块设计中。

5.4)点击块自动化运行在绿色的旗帜。然后单击好吧在弹出的屏幕上。

这将创建一个新的以太网DMA IP块和一个时钟向导。

5.5)找到时钟向导axi_ethernet_0_refclk并连接clk_in1到ui_clk输出mig_7series_0块。

5.6)点击连接自动化运行在绿色的旗帜。检查所有自动化复选框,然后单击好吧.

您可能会收到关于过时自动化的警告。只是连接自动化运行在所有的自动化系统中。这将为DDR内存创建一个AXI Interconnect,为外围组件创建另一个AXI Interconnect。

6.连接中断

6.1)找到Concat阻止并双击它以打开其设置。

6.2)改变数量的端口来5.点击好吧.

Concat块接收中断输入并将它们发送给Microblaze控制器。

将下列连接路由到Concat块;顺序并不重要:

-中断在AXI计时器块。

-mm2s_introut和s2mm_introut在axi_ethernet_0_dma块。

-mac_irq和中断在axi_ethernet_0块。

7.验证设计并制作一个HDL包装器

7.1)点击重新布局按钮以重新排列模块设计。

7.2)选择验证设计.这将检查设计和连接错误。

在设计验证步骤之后,我们将继续创建一个HDL系统包装器。点击来源选项卡并找到您的块设计。

7.4)右击你的块设计和点击创建高密度脂蛋白包装.让Vivado管理包装和自动更新并点击好吧.

这将在VHDL中创建一个顶级模块,并允许您生成位流。

8.生成一些文件

8.1)在Vivado的顶部工具栏中,单击产生的比特流.这也可以在流导航器左边的面板,下面程序和调试.

如果你还没有保存你的设计,你会得到一个提示来保存块设计。

将开始生成位文件。工具会运行合成和实现.在合成和实现都成功完成后,将创建位文件。你会在项目窗口的右上角发现一个综合与实现的状态栏。

这个过程可以在任何地方进行5 - 60分钟这取决于你的电脑。

生成比特流后,屏幕上会弹出消息提示。在本演示中,您不必打开已实现的设计。点击取消.

9.导出硬件设计到SDK

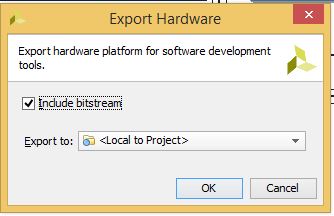

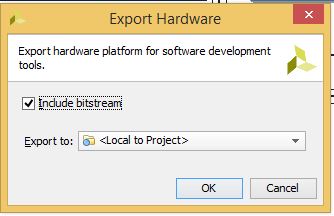

9.1)在主工具栏上,单击文件并选择出口的硬件.勾选复选框包括比特流并点击好吧.这将为软件开发工具- Vivado SDK导出带有系统包装的硬件设计。

将在下面创建一个新的文件目录echo_server。SDK类似Vivado硬件设计项目的名称。另外两个文件,.sysdef和.hdf也创造了。这个步骤实际上创建了一个新的SDK工作区。

9.2)在主工具栏上,单击文件然后发射SDK.将这两个下拉菜单保留为默认值本地项目并点击好吧.这将打开Xilinx SDK并导入硬件。

10.在Xilinx SDK

10.1) HW设计规范和包含的IP块显示在system.hdf文件。Xilinx SDK独立于Vivado,也就是说,从这里开始,你可以在导出的HW设计上用C/ c++创建你的SW项目。如果需要,还可以直接从Vivado Project主目录中创建的SDK文件夹中启动SDK。

从这里开始,如果你需要返回Vivado并对HW设计进行更改,那么建议关闭SDK窗口并在Vivado中进行所需的HW设计编辑。在此之后,您必须遵循创建新的HDL包装器、保存设计和位文件生成的顺序。然后必须将这个新的位文件和系统包装器导出到SDK。

10.2)中Project Explorer选项卡,您可以看到您的硬件平台。

系统是在Vivado中创建的块设计的名称。该硬件平台包含了所有的HW设计定义、已添加的IP接口、外部输出信号信息和本地存储地址信息。

11.在SDK中创建新的应用项目

11.1)点击新下拉箭头并选择应用程序项目.

为项目指定一个没有空格的名称,然后单击下一个.

11.2)选择lwIP回显服务器从模板列表中单击好吧.

将在。中看到两个新文件夹Project Explorer面板。

-

echo_server它包含所有的二进制文件,.C和.H(头文件)

-

echo_server_bsp哪个是板支持文件夹

echo_server是我们的主要工作源文件夹。这里还包含一个重要的文件,即“lscript.ld”。这是一个Xilinx自动生成的链接器脚本文件。双击此文件打开。

11.3)回到Project Explorer,双击并打开system.mss下echo_server_bsp文件夹中。点击修改BSP的设置.

11.4)点击lwip141然后找到temac_adapter_options然后点击箭头。找到phy_link_speed并将Value更改为CONFIG_LINKSPEED100.如果您的路由器支持千兆传输,请将此值更改为CONFIG_LINKSPEED1000.点击好吧.

12.用位文件编程FPGA

确保Genesys2是打开的,并通过两个连接到主机PCJTAGUSB端口和的UARTUSB端口。

在顶部工具栏上,单击FPGA程序按钮。

12.2)点击程序使用硬件设计对FPGA进行编程。

13.设置UART终端

13.1)打开一个串行终端应用程序(Tera术语)。连接到Genesys2 UART端口,波特率为9600。通过双击Uartlite模块,可以在模块设计中改变波特率。

14.编写Microblaze处理器程序

14.1)在开始之前,确保你已经将Genesys2插入路由器。

14.2)回到SDK,选择您的echo_server项目,然后单击运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

14.3)你的程序将运行,你应该看到IP信息在你的串行终端。

14.4)打开另一个终端连接回显服务器,连接回显服务器端口7上的单板IP.

14.5)通过在终端中输入一些东西来测试你的echo服务器。根据您的设置,您可能不会看到字符,直到您按下输入.当您这样做时,消息将被发送到Echo服务器,并将被回显到您的终端!

添加IP按下并搜索Microblaze.

添加IP按下并搜索Microblaze.

重新布局按钮以重新排列模块设计。

重新布局按钮以重新排列模块设计。

验证设计.这将检查设计和连接错误。

验证设计.这将检查设计和连接错误。

产生的比特流.这也可以在流导航器左边的面板,下面程序和调试.

产生的比特流.这也可以在流导航器左边的面板,下面程序和调试.

新下拉箭头并选择应用程序项目.

新下拉箭头并选择应用程序项目.

FPGA程序按钮。

FPGA程序按钮。

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.