开始使用Digilent Pmod ip

重要!

本指南使用Vivado 2015.4,与Xilinx软件的新版本相比,该指南的图像将过时。看到Getting Started with Digilent Pmod IPs 2018.2 edition浏览更多最新资料。

概述

Digilent提供了几个ip,这些ip被设计成尽可能简单地在FPGA上实现和使用Pmod。本指南将描述如何在Vivado Microblaze或Zynq设计中使用Pmod IP核。

在本教程的最后,您将有一个Vivado设计和演示您的FPGA或Zynq平台,使用Digilent Pmod IP核。

下面的两个下拉表显示了本教程支持哪些平台和Pmods,以及完成本教程所需了解的每个平台的一些细节。

请注意:关于设计中包含多个Pmod IP实例的问题已被报告。对于需要一个以上Pmod的项目(例如,两个Pmod NAVs),请使用Vivado 2017.4。

- 平台支持

-

平台 处理器类型 附庸风雅的 Microblaze 附庸风雅的S7 Microblaze 艺术Z7 Zynq Basys3 Microblaze Cmod A7 Microblaze Genesys2 Microblaze Nexys4 Microblaze Nexys4-DDR Microblaze 在下视频 Microblaze Zybo Zynq Zybo Z7 Zynq

- Pmods支持

-

Pmod 接口类型 参考时钟频率(兆赫) 时钟信号名称 中断销名称/ s 使用PmodGPIO 额外的笔记 8 ld GPIO - - - 是的 - ACL SPI 80 ext_spi_clk - - - ACL2 SPI 50 ext_spi_clk - - - AD1 SPI - - - - - AD2 IIC - - - - - AD5 SPI 50 - - - - 肌萎缩性侧索硬化症 SPI 50 ext_spi_clk - - - AMP2 GPIO - - timer_interrupt - - aq IIC - - - - - BB GPIO - - - 是的 - BT2 UART - - - - - BTN GPIO - - - 是的 - 可以 SPI One hundred. ext_spi_clk SPI_interruptGPIO_interrupt - CLS SPI 50 ext_spi_clk - - - CMPS2 IIC - - - - SDK项目需要数学库 颜色 IIC - - - - - DA1 SPI 50 ext_spi_clk - - - DHB1 脉宽调制/GPIO - - - - - DPG1 SPI 50 ext_spi_clk - - - 内附 GPIO - - - - - 全球定位系统(GPS) UART - - gps_uart_interrupt - - 陀螺 SPI 50 ext_spi_clk - - - HYGRO IIC - - - - - JSTK SPI 16 ext_spi_clk - - - JSTK2 SPI 16 ext_spi_clk - - - KYPD GPIO - - - - - 领导 GPIO - - - 是的 - MAXSONAR GPIO - - - - - MicroSD 使用Pmod SD IP核 - mtd SPI - - - - - 导航 SPI /GPIO 50 ext_spi_clk - - - OLED SPI /GPIO - - - - - OLEDrgb SPI /GPIO 50 ext_spi_clk - - - PIR GPIO - - - - - R2R GPIO - - - - - RTCC IIC - - - - - SD SPI - - - - - SF3 SPI 50 ext_spi_clk QSPI_INTERRUPT - - 苏维埃社会主义共和国 GPIO - - - 是的 - SWT GPIO - - - 是的 - TC1 SPI 50 ext_spi_clk - - TMP3 IIC - - - - 无线网络 SPI - - WF_INTERRUPT - 需要385 KB的BRAM或DDR

先决条件

硬件

-

A支持Digilent 7系列FPGA或Zynq Board

-

USB电缆

-

一个或多个支持的Digilent Pmods

软件

-

Xilinx Vivado 2015.4或更新的Xilinx SDK

-

本教程使用Vivado 2015.4

-

其他版本的Vivado可以工作,但功能不能保证

-

-

Digilent板支持文件

-

遵循维基指南关于如何安装Vivado 2015的板支持文件。X

-

-

Digilent Vivado IP库

-

将介绍这些文件的安装步骤2本教程的。

重要的。

如果要使用的Pmod IP有一个README文件,请确保在开始本教程之前查看它。该文件可在vivado-library / ip / Pmods /“你pmod”目录中。

教程

1.创建一个全新的Microblaze/Zynq区块设计

- Microblaze

-

- Zynq

-

遵循“从Zynq开始”教程,以获得基本的Zynq块设计。

以Zynq区块设计为例。

2.添加Digilent库存储库

2.1)找到Digilent的最新版本vivado-library其中的版本号与正在使用的Vivado版本相匹配(例如:“v64.1 -1”是Vivado 2016.4的第一个版本)。下载vivado-library——<版本> . zip文件(不是一个源代码档案!),然后将该档案提取到一个令人难忘的位置。这个GitHub存储库包含大量用于Digilent板的IP核,包括Digilent的所有Pmod IP核和Pmod接口描述。

3.将Pmod添加到模块设计中

信息

此列表包含平台的board文件中定义的所有组件。您可以使用它轻松地插入与平台上的硬件(例如以太网端口或一般用途)一起工作的IP块领导.当您在步骤1.1中创建初始设计时,应该已经选择了其中的几个。

提示

几个比较简单的GPIOPmods可以与PmodGPIO IP Core一起使用。要查看这个IP核是否支持您的Pmod,请参阅概述部分本教程的。

4.连接自动化运行

5.连接参考时钟

根据所使用的平台,将参考时钟附加到Pmod IP核上是不同的。选择最适合描述平台的选项卡(请参阅概述部分如果你不知道的话)。

- Zynq

-

5.1)双击ZYNQ处理系统块重新自定义它。在左侧的菜单中,单击时钟配置.扩大PL织物时钟下拉并检查尚未检查的第一个FCLK_CLK以激活它。将请求的频率设置为Pmod所需的频率。这个频率可以在Pmod兼容性图表中找到概述部分本教程的。点击好吧.

提示

如果已经检查的其中一个FCLK_CLK的频率与您的pmod所需的频率相匹配,则可以使用该时钟。将一个时钟连接到多个目的地是可能的。

- MicroBlaze与米格

-

5.1)双击mig_7series块重新定制它。在Xilinx内存接口生成器窗口中,继续单击下一个直到你看到选择额外的时钟(如下所示)。单击此框并选择您的Pmod所需的频率或最近的可用较慢的频率。所需的频率可以在Pmod兼容性图中找到概述部分本教程的。

提示

如果已经在使用其他时钟,并且其频率与您的Pmod所需的频率相匹配,那么您可以使用该时钟。将一个时钟连接到多个目的地是可能的。如果是这样,你可以取消退出MIG配置对话框。

5.2)请点击下一个.当你到达引脚选择屏幕时,点击验证然后好吧.继续点击下一个.点击接受在许可协议屏幕上,然后继续单击下一个.一旦你到达终点,点击生成用额外的时钟来再生你的米格机方块。

- MicroBlaze没有米格

-

5.1)双击时钟向导IP块重新自定义它。在定制对话框中,选择Output Clocks选项卡。检查尚未检查的下一个时钟以激活它。将请求的输出频率设置为Pmod所需的频率。这个频率可以在Pmod兼容性图表中找到概述部分本教程的。点击好吧.

提示

如果已经在使用其他时钟,并且其频率与您的Pmod所需的频率相匹配,那么您可以使用该时钟。将一个时钟连接到多个目的地是可能的。

6.连接中断

根据所使用的平台,将Pmod IP核中断附加到处理器是不同的。选择最适合描述平台的选项卡(请参阅概述部分如果你不知道的话)。

- Zynq

-

6.2)添加一个ConcatIP核块设计。重新定制concat块,以确保输入的数量与连接Zynq处理器所需的中断数量相匹配——可能只有一个。点击好吧.

- Microblaze

-

6.2)在块设计中增加一个Concat IP核。重新自定义concat块,以确保输入的数量与连接Microblaze处理器所需的中断数量相匹配——可能只有一个。点击好吧.

7.验证设计

7.1)点击重新布局按钮以重新排列模块设计。

7.2)选择验证设计.这将检查设计和连接错误。

7.3)如果你已经为你的块设计创建了一个HDL包装器,作为特定电路板的一部分开始使用……教程,跳过此步骤的其余部分。否则,在设计验证步骤之后,我们将继续创建一个HDL System Wrapper。点击来源选项卡并找到您的块设计。

7.4)右击你的块设计和点击创建高密度脂蛋白包装.让Vivado管理包装器并自动更新它并单击好吧.

这将在VHDL中创建一个顶级模块,并允许您生成位流。

8.生成位文件

将开始生成位文件。工具会运行合成和实现.在成功完成这两项之后,将创建位文件。你会在项目窗口的右上角发现一个综合与实现的状态栏。

这个过程可以在任何地方进行5 - 60分钟取决于你的电脑和目标板。

生成比特流后,屏幕上会弹出消息提示。在本演示中,您不必打开已实现的设计。点击取消.

9.导出硬件设计到SDK

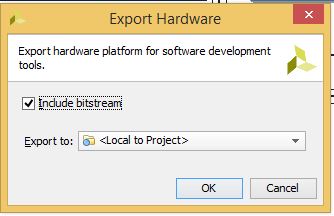

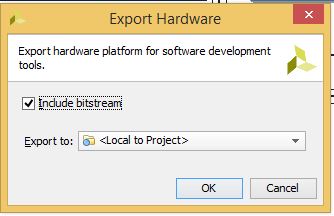

9.1)在主工具栏上,单击文件并选择出口的硬件.勾选复选框包括比特流并点击好吧.这将为软件开发工具Xilinx SDK导出带有系统包装器的硬件设计。

下面的项目目录将创建一个新的文件目录echo_server。SDK类似Vivado硬件设计项目的名称。另外两个文件,.sysdef和.hdf也创造了。这个步骤实际上创建了一个新的SDK工作区。

9.2)在主工具栏上,单击文件然后发射SDK.将这两个下拉菜单保留为默认值本地项目并点击好吧.这将打开Xilinx SDK并导入硬件。

10.旅游Xilinx SDK

HW设计规范和包含的IP块显示在system.hdf文件。Xilinx SDK独立于Vivado,也就是说,从这里开始,你可以在导出的HW设计上用C/ c++创建你的SW项目。如果需要,您还可以直接使用在主Vivado Project目录中创建的.SDK文件夹作为工作区启动SDK。从这里开始,如果你需要返回Vivado并对HW设计进行更改,那么建议关闭SDK窗口并在Vivado中进行所需的HW设计编辑。在此之后,您必须遵循保存设计的顺序,允许Vivado重新生成您的HDL包装器,并生成一个新的位文件。然后必须将这个新的位文件导出到SDK。

在Project Explorer选项卡,您可以看到您的硬件平台。系统是在Vivado中创建的块设计的名称。该硬件平台包含了所有的HW设计定义、已添加的IP接口、外部输出信号信息和本地存储地址信息。

Pmod IP设备的驱动程序可以在下面的硬件平台的适当文件夹中找到/驱动程序.如果你想编辑这些驱动程序,使用在你的板支持包下找到的版本libsrc.如果您确实修改了驱动程序,请记住,对硬件的任何更改都将覆盖这些更改,以及任何使用再生BSP来源.

11.在SDK中创建一个新的应用程序项目

将在。中看到两个新文件夹Project Explorer面板。

-

你的应用项目包含所有的二进制文件,.C和.H(头文件)

-

您的项目的板支持包,其中包含您的项目可能包括的驱动程序源文件

我们的主要工作源文件夹还包含一个重要的文件,如图所示,它是“lscript.ld”。这是一个Xilinx自动生成的链接器脚本文件,其中包括关于块设计中不同IP组件的内存地址的信息,以及其他内存区域的大小。

12.导入示例项目

13.用位文件编程FPGA

确保您的单板是打开的,并使用微型USB线连接到主机PC进行UART和编程。在一些板上,您只需要连接一个PROG/UART端口,而在其他板上,您将需要将您的PC连接到两个不同的端口,通常命名为UART和PROG或JTAG。在顶部工具栏上,单击FPGA程序按钮。有些电路板还需要连接到单独的电源。

13.2)点击程序使用硬件设计对FPGA进行编程。

14.编写Microblaze/ZYNQ处理器程序

14.1)大多数演示需要您使用PC上的串行终端来读取演示打印的消息。终端的设置将取决于你的板,但通常你将需要使用波特率115200或9600,8位数据,没有奇偶校验位,和一个停止位。Zynq项目将使用115200波特率,而MicroBlaze项目的波特率将取决于Vivado中Uartlite IP的配置。

14.2)选择您的应用程序项目并单击运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

14.3) Xilinx SDK将在Microblaze/Zynq处理器上运行main.c中启动的程序。查看示例主文件顶部的注释头,以获得关于演示的更多信息,以及任何额外的设置要求。

重新布局按钮以重新排列模块设计。

重新布局按钮以重新排列模块设计。

验证设计.这将检查设计和连接错误。

验证设计.这将检查设计和连接错误。

产生的比特流.这也可以在流导航器左边的面板,下面程序和调试.如果你还没有保存你的设计,你会得到一个提示来保存块设计。

产生的比特流.这也可以在流导航器左边的面板,下面程序和调试.如果你还没有保存你的设计,你会得到一个提示来保存块设计。

新下拉箭头并选择应用程序项目.

新下拉箭头并选择应用程序项目.

FPGA程序按钮。有些电路板还需要连接到单独的电源。

FPGA程序按钮。有些电路板还需要连接到单独的电源。

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.

运行……按钮。选择在硬件上启动(系统调试器)并点击好吧.