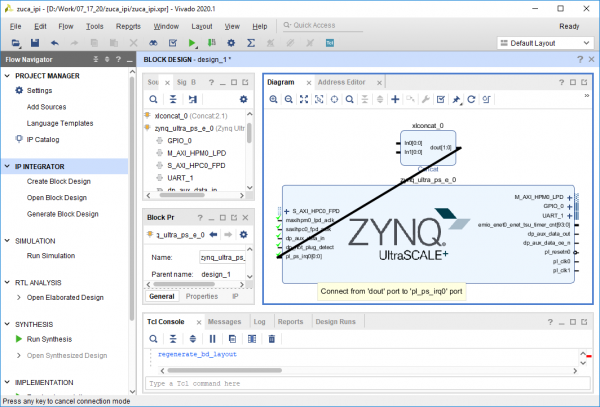

在块设计中添加Zynq UltraScale处理器

Zynq UltraScale+ MPSoC IP代表了Zynq UltraScale芯片的非fpga组件,被称为处理系统(Processing System)或PS。它必须用于一个模块设计,想要连接到处理器上的任何东西,并配置PS侧外设、时钟和其他设置。

注意:本节仅适用于带有Zynq UltraScale+芯片的单板。

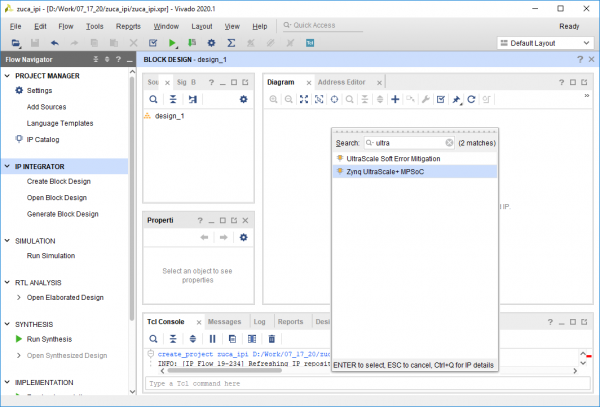

在方框图窗格的工具栏中,单击添加IP按钮( ).

).

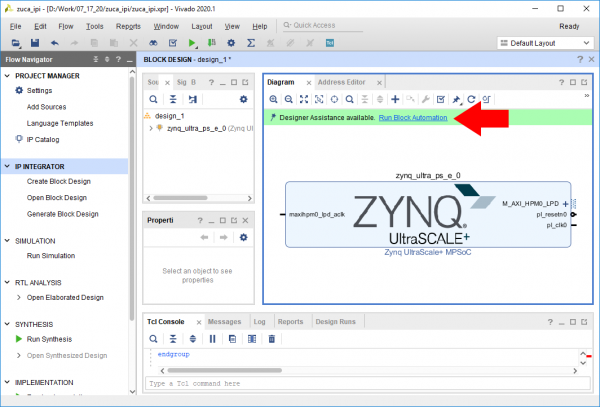

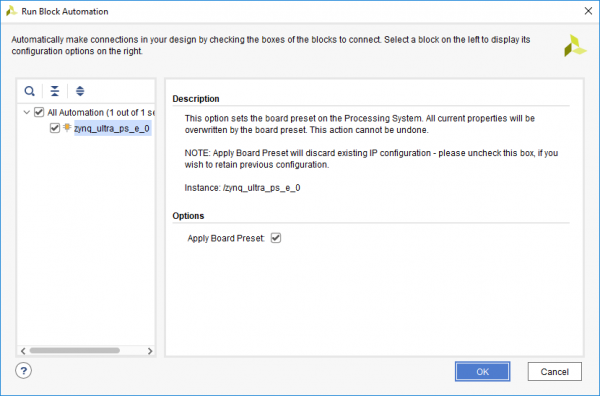

项目的需要可能要求您更改PS的一些默认设置。要编辑其设置,双击它以打开配置向导。

以下是两个具体案例:

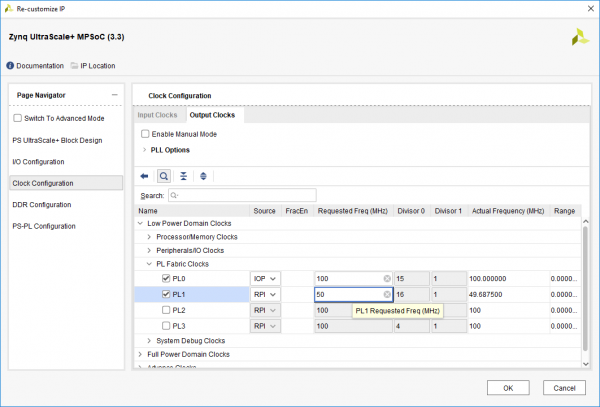

PS可以生成多个时钟,然后提供给FPGA结构。这些时钟被称为PL时钟,可以在时钟配置页签。它们位于低功率域时钟→PL织物时钟下拉。它们可以通过复选框启用(或禁用),用来驱动时钟的硬件源可以更改,频率可以修改。

Digilent Zynq UltraScale板的板文件默认情况下至少启用一个低功耗域PL时钟,用于连接MPSoC的M_AXI_HPM0_LPD端口的外设。

有些设计可能需要在设计中添加特定频率的额外时钟。在这些情况下,启用第二个时钟并指定所需的频率,如右图所示。

注意:这个部分总是可以在以后返回,因为在硬件构建之前可以随时执行附加时钟的添加。

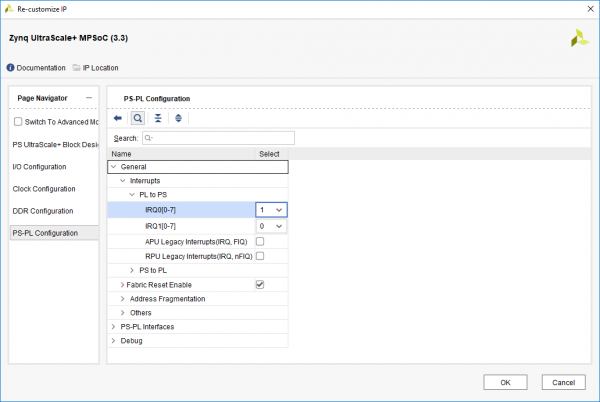

UltraScale设备也可以使用FPGA结构中产生的中断来触发处理系统中的中断。可以在配置向导中更改与中断相关的设置PS-PL配置选项卡。这些中断可以使用IRQ0端口,可以在一般→中断→PL对PS下拉。要启用该端口,IRQ0下拉菜单应该设置为“1”。